### ASSIGNMENT OF MASTER'S THESIS

| Title:           | Deadline Verification Using Model Checking |

|------------------|--------------------------------------------|

| Student:         | Bc. Jan Onderka                            |

| Supervisor:      | doc. DiplIng. Dr. techn. Stefan Ratschan   |

| Study Programme: | Informatics                                |

| Study Branch:    | Design and Programming of Embedded Systems |

| Department:      | Department of Digital Design               |

| Validity:        | Until the end of winter semester 2020/21   |

#### Instructions

The objective of the thesis is to write a model checker for proving that a given program in machine code for the 8-bit processor ATmega328p reacts within a given time bound to certain user-defined events. In addition, the design of the model checker should allow easy extension to further RISC processors.

Methodology:

1) Search for possible approaches to this problem in the literature.

2) Implement a first version of the model checker that is designed to return sound results, but is not necessarily efficient.

3) Test the model checker against benchmarks.

4) Find algorithmic improvements for increasing the efficiency of the model checker.

5) Implement and test the improvements. Check against alternative approaches.

6) Document the result and release as open source software.

#### References

Will be provided by the supervisor.

doc. Ing. Hana Kubátová, CSc. Head of Department doc. RNDr. Ing. Marcel Jiřina, Ph.D. Dean

Prague July 30, 2019

Master's thesis

### Deadline Verification Using Model Checking

Bc. Jan Onderka

Department of Digital Design Supervisor: doc. Dipl.-Ing. Dr. techn. Stefan Ratschan

May 28, 2020

### Declaration

I hereby declare that the presented thesis is my own work and that I have cited all sources of information in accordance with the Guideline for adhering to ethical principles when elaborating an academic final thesis.

I acknowledge that my thesis is subject to the rights and obligations stipulated by the Act No. 121/2000 Coll., the Copyright Act, as amended. In accordance with Article 46 (6) of the Act, I hereby grant a nonexclusive authorization (license) to utilize this thesis, including any and all computer programs incorporated therein or attached thereto and all corresponding documentation (hereinafter collectively referred to as the "Work"), to any and all persons that wish to utilize the Work. Such persons are entitled to use the Work in any way (including for-profit purposes) that does not detract from its value. This authorization is not limited in terms of time, location and quantity.

In Prague on May 28, 2020

. . . . . . . . . . . . . . . . . . .

Czech Technical University in Prague

Faculty of Information Technology

© 2020 Jan Onderka. All rights reserved.

This thesis is school work as defined by Copyright Act of the Czech Republic.

Into thesis is school work as defined by Copyright Act of the Czech Republic. It has been submitted at Czech Technical University in Prague, Faculty of Information Technology. The thesis is protected by the Copyright Act and its usage without author's permission is prohibited (with exceptions defined by the Copyright Act).

### Citation of this thesis

Onderka, Jan. *Deadline Verification Using Model Checking*. Master's thesis. Czech Technical University in Prague, Faculty of Information Technology, 2020.

### Abstrakt

V této práci je představena nová aplikace pro formální verifikaci splnění nejzazších termínů (deadlines) v jednoduchých programech pro mikrokontroléry, pracující na úrovni strojového kódu.

V práci jsou studovány dosavadní techniky a nástroje pro formální verifikaci. Jsou identifikovány jejich slabé stránky. Nevýhodou verifikačních technik pracujících na úrovni zdrojového kódu je zejména jejich neschopnost zaručit časy provádění na úrovni cyklů procesoru. Současných nástrojů pro verifikaci na úrovni strojového kódu je málo, nejsou široce dostupné a většinou jsou specificky navrženy pro konkrétní procesor, což velmi snižuje jejich užitečnost.

Aby nová aplikace nevykazovala nedostatky stávajících řešení, je navržen a implementován nový hybridní verifikační přístup. Techniky ověřování modelu na úrovni strojového kódu jsou použity pro reprezentaci stavového prostoru a verifikaci dodržení specifikace. Paměť mikrokontroléru a chování v rámci kroku jsou specifikovány pomocí jednoduchého imperativního jazyka, s kterým je možné manipulovat pomocí standardních technik na úrovni zdrojového kódu. Tím je umožněna kontrola splnění nejzazších termínů na úrovni cyklů procesoru, rozšiřitelnost na další mikrokontroléry vedle již implementovaného ATmega328P a implementace pokročilých technik bez závislosti na konkrétním použitém procesoru.

Vedle základní funkcionality programu jsou implementovány pokročilé techniky pro zacházení s nedeterminismem, generování řídícího toku a redukci cest pro jednoduché cykly. Aplikace je testována pro prokázání její užitečnosti pro verifikaci splnění nejzazších termínů pro jednoduché programy. Je diskutován dopad použitých technik a jsou identifikovány slibné cesty pro další zlepšení.

Klíčová slova Ověřování modelu, ověřování splnění nejzazších termínů, formální verifikace mikrokontrolérů, formální verifikace na úrovni strojového kódu, přesnost na úrovni cyklů, hybridní technika, nedeterminismus, generování řídícího toku, redukce cest pro jednoduché cykly

### Abstract

In this thesis, a new utility is presented for performing formal deadline checking of simple microcontroller programs at machine code level.

The existing formal verification approaches and tools are studied and their weaknesses identified. Namely, source level techniques cannot guarantee cyclecount precise execution times, while machine code verification tools are few, not generally available, and usually heavily tailored to a specific processor, significantly reducing their usefulness.

To counteract the weaknesses of current microcontroller verification tools, a novel hybrid approach is proposed and implemented. Machine code level model checking techniques are used for state space representation and verification of adherence to specification. Microcontroller memory and step behaviour is specified using a simple imperative language that can be manipulated using standard source code level techniques. This allows cycle-count based deadline checking, simple extension to other microcontrollers in addition to the implemented ATmega328P, and implementation of advanced techniques without dependence on the actual processor used.

In addition to the core functionality, advanced techniques for handling nondeterminism, control flow generation, and simple cycle path reduction are implemented. The utility is tested, showing its usefulness for simple program deadline verification. The impact of various techniques used is discussed and promising future improvements are identified.

**Keywords** Model checking, deadline checking, microcontroller formal verification, machine code level, cycle-accuracy, hybrid technique, nondeterminism, control flow generation, simple cycle path reduction

# Contents

| In       | troduction                                                            | 1         |

|----------|-----------------------------------------------------------------------|-----------|

| 1        | Definitions of terms used                                             | 3         |

|          | 1.1 Systems, models and specifications                                | 3         |

|          | 1.2 Production process                                                | 4         |

|          | 1.2.1 Software development production process                         | 4         |

|          | 1.3 Verification and validation                                       | 6         |

|          | 1.4 Informal verification, testing                                    | 6         |

|          | 1.5 Formal verification, its advantages and limitations               | 7         |

|          | 1.6 Deadline checking using formal verification techniques $\ldots$ . | 8         |

| <b>2</b> | Approaches to formal program verification                             | 9         |

|          | 2.1 Formal proof techniques                                           | 9         |

|          | 2.2 Model checking                                                    | 10        |

|          | 2.2.1 Symbolic model checking                                         | 11        |

|          | 2.2.2 Abstract model checking                                         | 11        |

| 3        | Specifics of microcontroller code verification                        | 13        |

|          | 3.1 Source code verification                                          | 13        |

|          | 3.2 Binary code verification                                          | 14        |

| <b>4</b> | Current binary-level model checkers for microcontrollers              | 15        |

|          | 4.1 State Exploring Assembly Model Checker (StEAM)                    | 15        |

|          | 4.2 Estes                                                             | 15        |

|          | 4.3 Arcade. $\mu$ C (formerly [mc]square)                             | 16        |

| 5        | Goals for a new deadline verification utility                         | 19        |

| 6        | Deadline checker usage                                                | <b>21</b> |

|          | 6.1 Usage for visualisation                                           | 21        |

| 3.2  | Verification of adherence to specification                                                                                                                                                                                                                                                                                                     | $\frac{23}{24}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | -                                                                                                                                                                                                                                                                                                                                              | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | * *                                                                                                                                                                                                                                                                                                                                            | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| .4   | Programming language and external dependencies selection                                                                                                                                                                                                                                                                                       | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Dead | dline checker implementation structure                                                                                                                                                                                                                                                                                                         | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1  | Description language processing                                                                                                                                                                                                                                                                                                                | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 8.1.1 Array slicing                                                                                                                                                                                                                                                                                                                            | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 8.1.2 Alias variables                                                                                                                                                                                                                                                                                                                          | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 8.1.3 Individual bit indexing and slicing                                                                                                                                                                                                                                                                                                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 8.1.4 Control flow                                                                                                                                                                                                                                                                                                                             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.2  | Language processing                                                                                                                                                                                                                                                                                                                            | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.3  | Description language intermediate representation                                                                                                                                                                                                                                                                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.4  | Program binary loading                                                                                                                                                                                                                                                                                                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.5  | State space generation                                                                                                                                                                                                                                                                                                                         | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.6  | State space representation                                                                                                                                                                                                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.7  | Output generation                                                                                                                                                                                                                                                                                                                              | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.8  |                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.9  | Deadline checker                                                                                                                                                                                                                                                                                                                               | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Adv  | anced techniques implemented                                                                                                                                                                                                                                                                                                                   | <b>45</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ).1  |                                                                                                                                                                                                                                                                                                                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ).2  | * * 0                                                                                                                                                                                                                                                                                                                                          | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.3  |                                                                                                                                                                                                                                                                                                                                                | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ).4  | Simple cycle path reduction                                                                                                                                                                                                                                                                                                                    | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9.5  | Simple cycle tailored IR stepping                                                                                                                                                                                                                                                                                                              | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fost | ing the deadline checker                                                                                                                                                                                                                                                                                                                       | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | <b>4</b> 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| -0.2 |                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 10.2.5 Independent nondeterminism                                                                                                                                                                                                                                                                                                              | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0.3  | Qualitative testing                                                                                                                                                                                                                                                                                                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                                                | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      | 10.3.1 Blink                                                                                                                                                                                                                                                                                                                                   | $53 \\ 54$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | 5.3<br>Dead<br>7.1<br>7.2<br>7.3<br>7.4<br>Dead<br>5.1<br>5.2<br>5.4<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>0.1<br>0.2<br>0.3<br>0.4<br>0.2<br>0.3<br>0.4<br>0.2<br>0.3<br>0.4<br>0.2<br>0.3<br>0.4<br>0.2<br>0.3<br>0.4<br>0.2<br>0.3<br>0.4<br>0.2<br>0.3<br>0.4<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5 | 3       Interpretation of counterexamples and worst-case paths         3       State representation and nondeterminism handling         2       Specification description         3       State representation and nondeterminism handling         4       Programming language and external dependencies selection         5       Deadline checker implementation structure         1       Description language processing         8.1.1       Array slicing         8.1.2       Alias variables         8.1.3       Individual bit indexing and slicing         8.1.4       Control flow          2         2       Language processing          3         3       Description language intermediate representation          2          State space generation              4         Program binary loading           5         State space generation           6         State space representation           8         Deadline specification           9         < |

| 10.4.1 Blink10.4.2 Independent nondeterminism10.4.2 Independent nondeterminism10.5 Interpretation of results10.6 Comparison with other binary-level model checkers | $\frac{58}{59}$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Conclusion                                                                                                                                                         | 61              |

| Bibliography                                                                                                                                                       |                 |

| A Contents of enclosed SD card                                                                                                                                     |                 |

# **List of Figures**

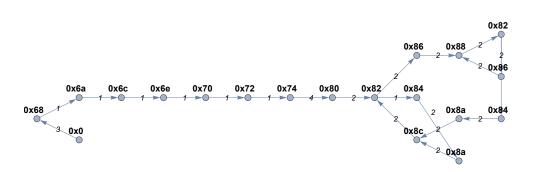

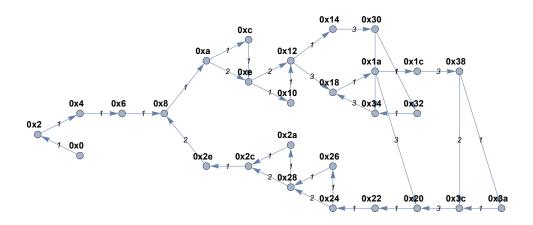

| 6.1  | State space graph of an example program generated by the imple-<br>mentation            | 22 |

|------|-----------------------------------------------------------------------------------------|----|

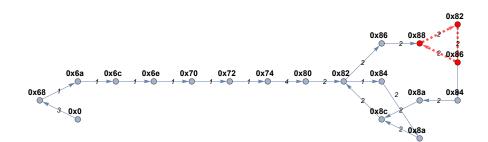

| 6.2  | Example specification rule counterexample generated by the im-                          | 25 |

| 6.3  | plementation          Example specification rule worst-case satisfaction path generated | 20 |

|      | by the implementation                                                                   | 25 |

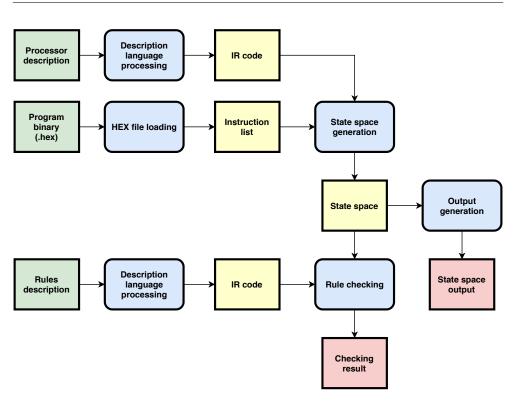

| 8.1  | Top-level view of implementation inputs, outputs and core modules                       | 34 |

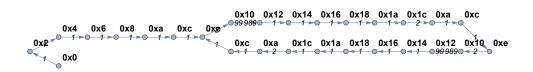

| 10.1 | Execution state graph generated for test program Blink when sim-                        |    |

|      | ple path reduction is used                                                              | 54 |

| 10.2 | Control flow graph generated for test program Gate array                                | 55 |

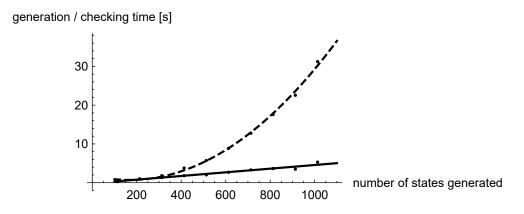

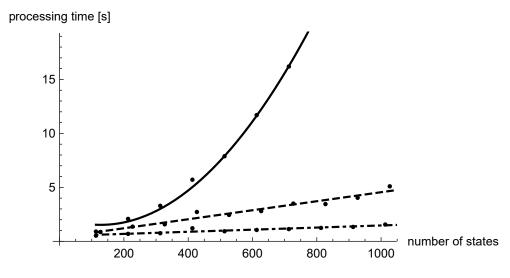

| 10.3 | Dependence of state space generation time and deadline checking                         |    |

|      | time on number of states when test program Blink is checked                             | 57 |

| 10.4 | Dependence of full deadline checker processing time on the number                       |    |

|      | of states when test program Blink is checked                                            | 57 |

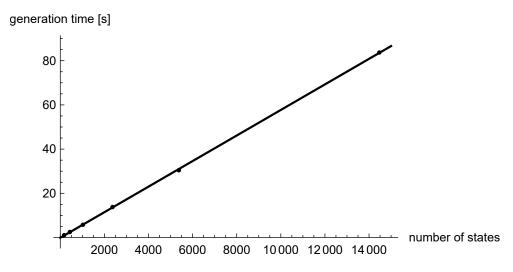

| 10.5 | Dependence of state space generation time on number of states                           |    |

|      | when independent nondeterminism test program is checked                                 | 58 |

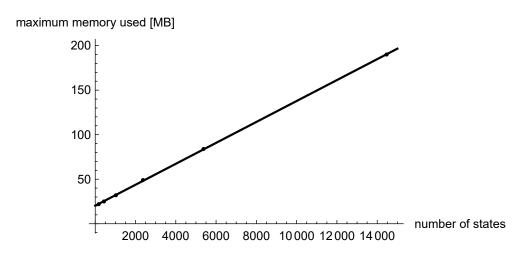

| 10.6 | Dependence of maximum memory used on number of states when                              |    |

|      | independent nondeterminism test program is checked                                      | 59 |

|      |                                                                                         |    |

# List of Tables

| 10.1 | Summary of results of test program Gate array deadline checking .     | 55 |

|------|-----------------------------------------------------------------------|----|

| 10.2 | Worst-case lengths of paths before satisfaction of rule eventual con- |    |

|      | sequences for test program Gate array                                 | 55 |

### Introduction

Modern computer systems are becoming increasingly more complex. As the manufacturing technology progresses, more powerful devices can be used to aid with increasingly more difficult tasks. Despite this, there is a large amount of simple tasks that do not require an abundant amount of resources. These tasks are usually fulfilled by embedded devices that are as simple as possible to minimize cost per unit and power consumption.

When the amount of produced devices is not large enough to warrant an application-specific integrated circuit (ASIC), microcontrollers are the uncrowned kings of this field. They require little to no external components, can be programmed to fulfill the developer's needs, their cost is very low thanks to the economy of scale, and so can be their power consumption if an appropriate part is selected and good design practices are followed.

Unfortunately for developers, just the fact that the programmed device seemingly performs its task well does not mean that it will continue to do so indefinitely. While a manufacturer may guarantee that the microprocessor itself will fulfill its specification while inside its operation envelope (with a certain probability and subject to errata), the program itself is a weak point.

Empirical methods (setting device inputs to selected values and determining whether the device reacts in an expected way) can only take one so far. If a bug is found, the program must be fixed. If no bugs are found using a combination of inputs, not much can be said about the program: a different input could make the program react in an unexpected way. This could have a serious impact, compromising the function of the device (and consequently, its reliability), security, safety, etc.

While this is considered to be an extremely important issue for safetycritical, security-critical, and ultra-reliable systems, I feel that not enough is done for typical, consumer-targeted devices. A single software bug may impact thousands or millions of devices. As many embedded systems are not easily reprogrammable by the user (e.g. by over-the-air reprogramming or manufacturer-aided reflashing via a USB port), this may lead to high product

#### INTRODUCTION

recall costs, damages to the company's reputation, excessive electronic waste (as many companies choose to lock the microcontrollers from reprogramming in order to protect their intellectual property) and other undesirable effects.

Blame should not be put on the product developers, however. Using formal verification techniques that guarantee that the program always works according its specification is currently difficult, requiring considerable work by highly trained specialists. Tools are expensive or severely limited in usefulness.

This is why I decided to create a formal verification tool that would be useful for verification of microcontroller programs that perform simple tasks (henceforth referred to as a "deadline checker" for brevity). Its outward simplicity should aid its adoption not just by professionals, but also by students and hobbyists. This should ultimately lead to a wider adoption of formal verification techniques (as the students and hobbyists become professionals) and better, less faulty embedded products.

I have been convinced from early on that the tool should not be tied to a specific microcontroller or an architecture. Selecting the best device for a task is an integral step in the product development process. A tool that forces the developer to use a certain microcontroller is clearly flawed. As I found out, this requirement for extensibility unfortunately drastically increases the internal complexity of the implementation. Fortunately, this is paid off by the general applicability of each improvement instead of relying on various kludges that only work in specific cases.

Usage of advanced techniques is paramount for avoiding state space explosion. Naïve techniques that perform verification by building the whole state space and examining it are only sufficient for a highly limited subset of programs. Most programs (even simple ones) use various constructs that make the state space impractically big and verification unacceptably slow. Thanks to the generality of the implementation, I was able to add some general techniques to combat these scenarios. More can be added in the future.

I shall further discuss the theoretical underpinnings used to develop the tool, current alternatives, and the tool itself. In Chapter 1, I discuss the terms I use when concerned with ensuring that a device actually does what it is supposed to do. In Chapter 2, I introduce approaches to formal verification (that is, checking that a specification truly holds for all inputs) with a focus on model checking. In Chapter 3, I discuss the specifics of formal verification of microcontroller programs as opposed to other levels and parts of systems that may be verified. In Chapter 4, I examine the current tools available in detail and the lessons I learned from them. In Chapter 5, I explain the precise goals that I chose to aim for during development. In Chapter 6, I describe usage of the tool from user's point of view. In Chapter 7, I discuss design choices made when developing the tool. In Chapter 9, I describe advanced techniques implemented. In Chapter 10, I determine how well the tool performs using simple testing programs and discuss areas for potential improvements.

### CHAPTER **I**

### Definitions of terms used

Many terms are commonly used concerning creation of devices that should behave in a certain way and determination of whether they actually do. Unfortunately, the exact definitions used are usually rather contentious, as seen and discussed in [1]. I shall therefore define how I use them in this thesis. The definitions are based on a "systems" point of view, particularly as used for embedded development. I shall also give an explanation of why I consider them to be the best fit for my purposes.

### 1.1 Systems, models and specifications

First, I introduce some core terms:

- A *physical system* is a "system" in the physical sense, i.e. "a group of things, pieces of equipment, etc. that are connected or work together" [2].

- A *model* is "a simple description of a system, used for explaining how something works or calculating what might happen, etc." [2].

- A conceptual model, also termed mental model, is a model comprised by a set of thoughts about the expected properties and behaviour of a physical system (e.g. what it should cost, what task it should fulfill, how should it react depending on an input).

- A *specification* is "a detailed description of how something is, or should be, designed or made" [2].

- A *requirements specification* is a specification that reflects the requirements imposed by the conceptual model.

- A system model is a model that can be, in an automated manner, converted to a manufacturing specification.

• A *manufacturing specification* is a specification that contains all needed information for manufacturing the actual physical system.

### **1.2** Production process

I find the aforementioned definitions most useful in the context of a *production process*. Its ultimate goal is production of an actual physical system that behaves according to the conceptual model. This process is divided into two stages, a *design process* and a *manufacturing process*. The design process is comprised by three steps and the manufacturing process by the fourth one:

- 1. The conceptual model is turned into a requirements specification.

- 2. The requirements specification is used to create a system model.

- 3. The system model is converted into a manufacturing specification.

- 4. The manufacturing specification is used to create the actual physical systems that may be sold to customers.

I consider the differences between the words *model* and *specification* to be rather semantic in nature: a model describes something, while a specification requires something to perform in a certain way. However, while one can create a product without actually writing down specifications (taking a rather informal approach), the conceptual model (what is wanted) and the system model (how it should work) cannot be skipped.

These definitions are not universally fit for everything and everyone. Mathematicians typically are not concerned with product development. They thus use different definitions, sometimes colliding with the previously discussed definitions (such as they do for the term *model*, which shall be further discussed in the context of model checking in Chapter 2). The production process becomes a bit different in software development, but the core ideas remain the same.

### 1.2.1 Software development production process

Traditional computer software (e.g. word processors, video editing software, computer games, web browsers, etc.) is not tightly coupled with the hardware that it runs on, using an abstraction layer such as operating system application programming interface (API). This is highly beneficial for common tools since it enables a single program to be run on a multitude of different devices, differing in processor capabilities, peripherals, etc. The production process for software becomes a bit muddled since the manufacturing process is no longer well defined. I consider the manufacturing process in the traditional software case to consist of running the program on the target machine, enabling the computer executing the program to become the physical system fulfilling the specifications. In this case, the previously defined terms have this correspondence:

- 1. The conceptual model is a set of ideas about how should a computer running the program should behave.

- 2. The requirements specification is a specification detailing the suitable computer configurations and usable APIs (*execution environment*) and the required behaviour of the compiled program when executed on one of these computer configurations.

- 3. The system model is the source code of the program paired with the knowledge of the guaranteed behaviour of the programming language used and execution environment.

- 4. The manufacturing specification is a compiled program binary. The actual physical system is created ("manufactured") by running the program binary on a suitable computer.

To enable further discussion of system model checking without excluding checking compiled program binaries, I note that they can be considered source code with an identity translation programming language.

These definitions are useful for me as they set up the notion is that actual software never exists in a vacuum: it must always be paired with a proper execution environment. This is a fundamental concept for my further discussion. By combining execution environment guarantees, the guarantees specified by the programming language used (in case the analysis is not performed on the machine code itself), and the program, it may be possible to prove or disprove some properties about this combination. Then, we might be certain that the actual system will behave as intended as long as all of the guarantees hold.

For microcontroller programs, the process is very similar to traditional software, with the important distinction that no APIs and abstraction layers are used for simple programs ("bare metal" programming). For more complex applications, a lightweight operating system may be used, such as FreeRTOS [3]. These operating systems usually are not a distinct program that executes other programs at its will, but behave like libraries in that they are compiled with the program, forming a single binary file to be uploaded to the microcontroller. These lightweight operating systems may therefore be considered a part of the program for analysis instead of being an external API. This practically means that for the resultant program, the execution environment is still the microcontroller and its peripherals, not some abstract APIs. The knowledge of processor behaviour is therefore crucial for determining interesting properties.

### **1.3** Verification and validation