# **BRNO UNIVERSITY OF TECHNOLOGY** VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

FACULTY OF INFORMATION TECHNOLOGY FAKULTA INFORMAČNÍCH TECHNOLOGIÍ

DEPARTMENT OF INTELLIGENT SYSTEMS ÚSTAV INTELIGENTNÍCH SYSTÉMŮ

# EMPLOYING APPROXIMATE EQUIVALENCE FOR DESIGN OF APPROXIMATE CIRCUITS

VYUŽITÍ PŘIBLIŽNÉ EKVIVALENCE PŘI NÁVRHU PŘIBLIŽNÝCH OBVODŮ

MASTER'S THESIS DIPLOMOVÁ PRÁCE

AUTHOR AUTOR PRÁCE Bc. JIŘÍ MATYÁŠ

SUPERVISOR VEDOUCÍ PRÁCE RNDr. MILAN ČEŠKA, Ph.D.

**BRNO 2017**

#### Zadání diplomové práce/19459/2016/xmatya05

Vysoké učení technické v Brně - Fakulta informačních technologií

Ústav inteligentních systémů

Akademický rok 2016/2017

# Zadání diplomové práce

Řešitel: Matyáš Jiří, Bc.

Obor: Inteligentní systémy

Téma: Využití přibližné ekvivalence při návrhu přibližných obvodů Employing Approximate Equivalence for Design of Approximate Circuits

Kategorie: Formální verifikace

### Pokyny:

- Seznamte se s myšlenkou využití evolučních technik pro automatickou syntézu přibližných aritmetických a logických obvodů a s existujícími konceptuálními návrhy využití technik formální verifikace pro posuzování míry shody přesného a přibližného obvodu.

- 2. Seznamte se s různými existujícími nástroji pro řešení SAT a SMT problémů, které jsou potenciálně využitelné v daném kontextu.

- 3. Zkonkretizujte do experimentálně ověřitelné podoby vybrané přístupy k využití formálních technik v daném kontextu a implementujte je.

- 4. Experimentálně ověřte na vhodně zvolených obvodech různé uvažované přístupy a podrobně diskutujte jejich výhody a nevýhody.

### Literatura:

- Holík, L., Lengál, O., Rogalewicz, A., Sekanina, L., Vašíček, Z., Vojnar, T.: Towards Formal Relaxed Equivalence Checking in Approximate Computing Methodology, In: Proc. of WAPCO'16, HiPEAC, 2016.

- Vizel, Y., Weissenbacher, G., Malik, S.: Boolean Satisfiability Solvers and Their Applications in Model Checking, Proceedings of the IEEE, 103(11), 2015.

- Chandrasekharan, A., Soeken, M., Grosse, D., Drechsler, R.: Precise error determination of approximated components in sequential circuits with model checking, In: Proc. of DAC '16, ACM, 2016.

Při obhajobě semestrální části projektu je požadováno:

První dva body zadání a alespoň začátek práce na bodě třetím.

Podrobné závazné pokyny pro vypracování diplomové práce naleznete na adrese http://www.fit.vutbr.cz/info/szz/

Technická zpráva diplomové práce musí obsahovat formulaci cíle, charakteristiku současného stavu, teoretická a odborná východiska řešených problémů a specifikaci etap, které byly vyřešeny v rámci dřívějších projektů (30 až 40% celkového rozsahu technické zprávy).

Student odevzdá v jednom výtisku technickou zprávu a v elektronické podobě zdrojový text technické zprávy, úplnou programovou dokumentaci a zdrojové texty programů. Informace v elektronické podobě budou uloženy na standardním nepřepisovatelném paměťovém médiu (CD-R, DVD-R, apod.), které bude vloženo do písemné zprávy tak, aby nemohlo dojít k jeho ztrátě při běžné manipulaci.

| Vedoucí:         | Češka Milan, RNDr., Ph.D., UITS FIT VUT |  |

|------------------|-----------------------------------------|--|

| Datum zadání:    | 1. listopadu 2016                       |  |

| Datum odevzdání: | 24. května 2017                         |  |

doc. Dr. Ing. Petr Hanáček vedoucí ústavu

# Abstract

This thesis is concerned with the utilization of formal verification techniques in the design of the functional approximations of combinational circuits. We thoroughly study the existing formal approaches for the approximate equivalence checking and their utilization in the approximate circuit development. We present a new method that integrates the formal techniques into the Cartesian Genetic Programming. The key idea of our approach is to employ a new search strategy that drives the evolution towards promptly verifiable candidate solutions. The proposed method was implemented within ABC synthesis tool. Various parameters of the search strategy were examined and the algorithm's performance was evaluated on the functional approximations of multipliers and adders with operand widths up to 32 and 128 bits respectively. Achieved results show an unprecedented scalability of our approach.

# Abstrakt

Tato práce je zaměřena na využití formálně verifikačních technik pro návrh funkčních aproximací kombinačních obvodů. Jsou zde důkladně prostudovány existující formální přístupy pro zkoumání přibližné ekvivalence a jejich použití při vývoji aproximovaných obvodů. V rámci této práce je navržena nová metoda, která integruje vybrané formální techniky do Kartézského genetického programování. Klíčovým bodem nového přístupu je využití prohledávací strategie, která vede evoluci směrem k řešením, která lze rychleji verifikovat. Navržený algoritmus byl implementován v rámci syntézního nástroje ABC. Jeho výkonnost byla otestována na vývoji funkčních aproximací násobiček a sčítaček s šířkami vstupních operandů 32, respektive 128 bitů. Dosažené výsledky ukazují výjimečnou škálovatelnost navržené metody.

## Keywords

Approximate circuits, relaxed equivalence, evolutionary circuit design, Cartesian genetic programming, ABC.

## Klíčová slova

Aproximované obvody, přibližná ekvivalence, evoluční návrh obvodů, Kartézské genetické programování, ABC.

# Reference

MATYÁŠ, Jiří. Employing Approximate Equivalence for Design of Approximate Circuits. Brno, 2017. Master's thesis. Brno University of Technology, Faculty of Information Technology. Supervisor RNDr. Milan Češka, Ph.D.

# Employing Approximate Equivalence for Design of Approximate Circuits

# Declaration

Hereby I declare that this master's thesis was prepared as an original author's work under the supervision of Dr. Milan Češka. The crucial information about evolutionary algorithms, experimental settings and circuit synthesis was provided by Dr. Zdeněk Vašíček and Ing. Vojtěch Mrázek. All the relevant information sources, which were used during preparation of this thesis, are properly cited and included in the list of references.

> Jiří Matyáš May 24, 2017

## Acknowledgements

I would like to thank Dr. Milan Češka for supervising and his active and professional approach to this thesis, Dr. Zdeněk Vašíček for providing information about evolutionary algorithms and Ing. Vojtěch Mrázek for the enormous help with the experimental evaluation of the results of this thesis.

# Contents

| <ul> <li>2 Evolution Based Approximate Circuit Design</li> <li>2.1 Approximation techniques</li></ul>                                                                                                                                                                                                                                                                                                                           | 3  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>2.1 Approximation techniques</li></ul>                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

| <ul> <li>2.2 Evolutionary algorithms</li> <li>2.3 Cartesian genetic programming</li> <li>2.3.1 Chromosome representation</li> <li>2.3.2 Genetic operators</li> <li>2.3.3 CGP pseudocode</li> <li>2.4 Fitness function and error metrics</li> <li>2.4.1 Fitness evaluation methods</li> <li>3 Formal Methods for Fitness Evaluation</li> <li>3.1 Basic verification techniques</li> <li>3.1.1 Explicit Model Checking</li> </ul> |    |

| <ul> <li>2.3 Cartesian genetic programming</li></ul>                                                                                                                                                                                                                                                                                                                                                                            |    |

| <ul> <li>2.3.1 Chromosome representation</li></ul>                                                                                                                                                                                                                                                                                                                                                                              |    |

| <ul> <li>2.3.2 Genetic operators</li></ul>                                                                                                                                                                                                                                                                                                                                                                                      |    |

| <ul> <li>2.3.3 CGP pseudocode</li></ul>                                                                                                                                                                                                                                                                                                                                                                                         |    |

| <ul> <li>2.4 Fitness function and error metrics</li></ul>                                                                                                                                                                                                                                                                                                                                                                       |    |

| <ul> <li>2.4.1 Fitness evaluation methods</li></ul>                                                                                                                                                                                                                                                                                                                                                                             |    |

| <ul> <li>3 Formal Methods for Fitness Evaluation</li> <li>3.1 Basic verification techniques</li></ul>                                                                                                                                                                                                                                                                                                                           |    |

| 3.1    Basic verification techniques                                                                                                                                                                                                                                                                                                                                                                                            | 10 |

| 3.1.1 Explicit Model Checking                                                                                                                                                                                                                                                                                                                                                                                                   | 15 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 3.1.2 Symbolic model checking                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.2 Verification through satisfiability checking                                                                                                                                                                                                                                                                                                                                                                                |    |

| 3.2.1 SAT                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.2.2 SMT                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.3 Strict equivalence miters                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.3.1 ABC                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| 3.4 Approximate equivalence miters                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 3.4.1 N-th bit error $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                   | 23 |

| 3.4.2 N-th bit error with counterexamples                                                                                                                                                                                                                                                                                                                                                                                       | 23 |

| 3.4.3 Miter with subtractor and absolute value result                                                                                                                                                                                                                                                                                                                                                                           | 24 |

| 3.4.4 Sequential miters                                                                                                                                                                                                                                                                                                                                                                                                         | 25 |

| 4 Scalable Approximate Circuit Design                                                                                                                                                                                                                                                                                                                                                                                           | 28 |

| 4.1 Miter with subtractor and two's complement result                                                                                                                                                                                                                                                                                                                                                                           | 28 |

| 4.2 Miter with subtractor and comparator                                                                                                                                                                                                                                                                                                                                                                                        | 29 |

| 4.3 Verifiability-driven search strategy                                                                                                                                                                                                                                                                                                                                                                                        |    |

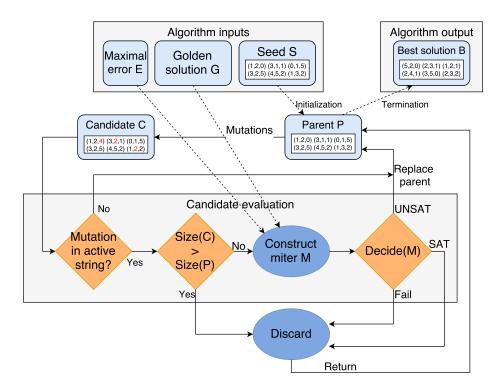

| 4.4 Improved evolutionary loop                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 4.4.1 Mutations in active string detection                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 4.4.2 Candidate area approximation                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 5 Implementation in ABC                                                                                                                                                                                                                                                                                                                                                                                                         | 35 |

| 5.1 Circuit representation formats                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 5.2 CGP configuration                                                                                                                                                                                                                                                                                                                                                                                                           | 36 |

|              | 5.3                   | Miter construction                               | 37        |  |  |  |

|--------------|-----------------------|--------------------------------------------------|-----------|--|--|--|

|              | 5.4                   | Satisfiability check procedure                   | 38        |  |  |  |

|              | 5.5                   | Algorithm output and the best candidate solution | 40        |  |  |  |

|              | 5.6                   | Pareto front approximation                       | 41        |  |  |  |

| 6            | Exp                   | eriments and Results                             | 42        |  |  |  |

|              | 6.1                   | Experimental setup                               | 42        |  |  |  |

|              | 6.2                   | Performance comparison                           | 42        |  |  |  |

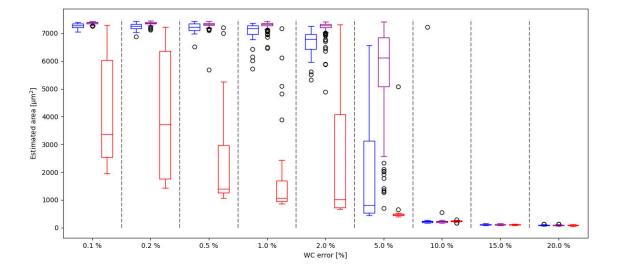

|              |                       | 6.2.1 Proposed miter area comparison             | 43        |  |  |  |

|              | 6.3                   | The impact of limited SAT resources              | 43        |  |  |  |

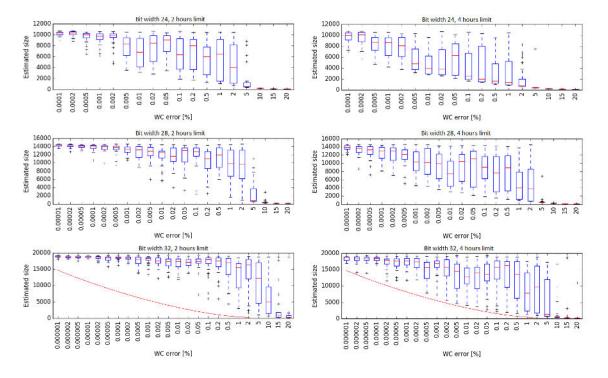

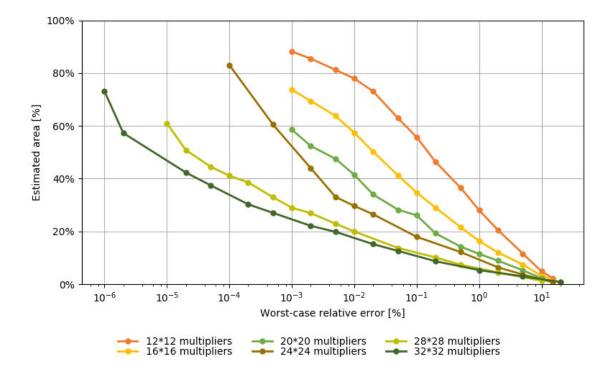

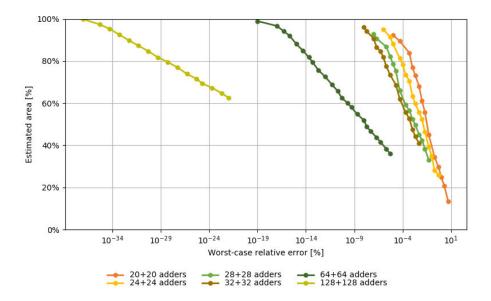

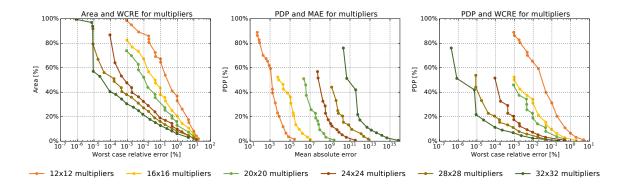

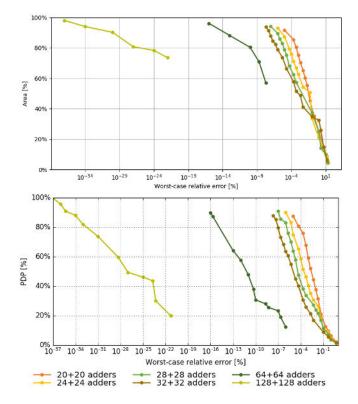

|              | 6.4                   | Approximate multipliers                          | 46        |  |  |  |

|              | 6.5                   | Approximate adders                               | 48        |  |  |  |

|              | 6.6                   | Circuit synthesis results                        | 48        |  |  |  |

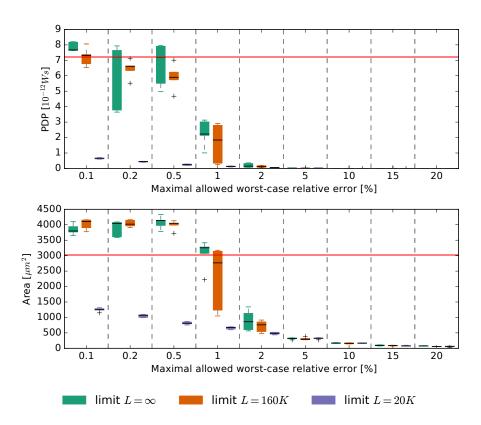

|              |                       | 6.6.1 SAT resource limit impact                  | 49        |  |  |  |

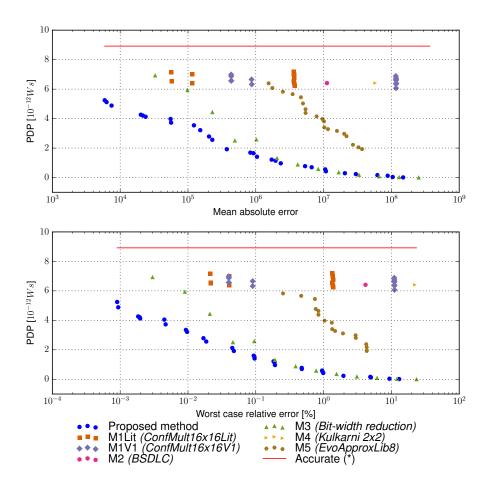

|              |                       | 6.6.2 16-bit multiplier comparison               | 49        |  |  |  |

|              |                       | 6.6.3 Complex approximate multipliers synthesis  | 50        |  |  |  |

|              |                       | 6.6.4 Complex approximate adders synthesis       | 51        |  |  |  |

| 7            | Con                   | clusion                                          | <b>53</b> |  |  |  |

| Bi           | bliog                 | graphy                                           | <b>54</b> |  |  |  |

| $\mathbf{A}$ | Exa                   | mple configuration file                          | 56        |  |  |  |

| в            | B Example log file 57 |                                                  |           |  |  |  |

# Chapter 1

# Introduction

Approximate computing has been recently established as a new research field in computer science. Its main purpose is to examine, how computer systems could be made better by relaxing the requirement, that they are always performing exactly correct computations. Approximate computing can be employed in so called *error resilient* applications. These applications can produce acceptable results despite the fact that their underlying computations are performed imperfectly (with errors). This can be caused by various factors: errors average out, errors are not recognizable by limited human perception capabilities, no golden solution is available for validation of the results or users are willing to accept some inaccuracies under special circumstances. The practical applications featuring these attributes include image and multimedia processing, signal processing, data mining, machine learning, neural networks and scientific computing. For example, Google uses this approach in their Tensor processing unit [8]. In general, most of these applications are highly computation intensive and their implementations consume significant amount of energy.

There are three major approaches for performing approximate computing. Approximate circuits, such as adders or multipliers, can reduce hardware size or computation time. Approximate storage stores approximate values of data (e.g. by truncating less significant bits) instead of saving the exact values or uses less reliable memory. Software approximation includes techniques such as loop perforation [14] (some loop iterations viewed as unnecessary can be skipped), memoization, task skipping (skipping tasks similarly to loop skipping) and Monte Carlo algorithms [15]. This thesis further focuses on the first method mentioned – approximate circuits.

There are different techniques for approximate circuit design: over-scaling, over-clocking and functional approximation. This thesis aims at functional approximation where we try to approximate the logic functions computed by the correct circuits. The approximate circuits are designed in such a way that their results are sufficiently similar to the original specification.

Developing accurate and effective approximate circuits is a very challenging task. Basic techniques are usually limited to small combinational and sequential circuits [12, 22] (tens to hundreds of logical gates) and struggle to develop larger circuits, where the evaluation of circuit accuracy becomes computationally unfeasible [25]. There are many different approaches improving the development of approximate circuits that have been examined recently. New methodologies, such as SALSA [27] or SASIMI [26], start with a golden circuit specification and a quality constraint that defines the amount of error to be introduced into the implementation. SALSA then synthesizes an approximate version of the circuit by modifying the original version. The final circuit has to satisfy the defined constraints.

This thesis focuses on approximate circuit design based on evolutionary algorithms [2]. This approach relies on the iterative generation and evaluation of a huge number of candidate solutions. It is crucial to be able to quickly assess the quality (fitness) of a candidate solution in order to find useful approximate circuits. Conventional approaches to fitness evaluation compare the results of the candidate solution to the expected golden results for all possible input combinations. Even though this process can be sped up significantly using a parallel evaluation technique, the task is still unfeasible for larger circuits. For example, with 32-bit multiplier, we need to evaluate  $2^{64}$  different input combinations which is a computationally unfeasible task. To solve this problem, a statistical approach evaluating only a subset of all possible inputs can be utilized. However, this technique called random simulation does not provide any guarantees on the approximation error.

To solve this problem, we employ formal verification methods. Formal verification is used to prove or disprove correctness of a system with respect to a given specification using rigorous mathematical methods. We try to convert the problem of fitness evaluation into a formal description and then employ the verification methods to assess the value of the fitness function. In order to determine the error of a candidate solution, we encode both the candidate and the golden solution into an instance of the formal problem. The two solutions are combined using a special construction – miter [5, 19]. The simplest of miters performs the strict equivalency check, which is not suitable for the approximate circuit development. Therefore more complex miters performing relaxed equivalence checking are designed in order to check the fitness function of an approximate solution [5].

There are many different formal verification tools and algorithms that can be used for fitness evaluation. The ABC synthesis tool [13] is an open source software for synthesis and verification of digital combinational and sequential circuits. It provides efficient implementation of several verification and optimization algorithms as well as various formats and functions for circuit synthesis and manipulation. Because of its open source nature, we employ the existing code base to implement the proposed algorithm.

#### Contributions

The main contribution of this thesis is the proposal of a method which allows to approximate complex arithmetic circuits with formal guarantees on the approximation error. The method integrates formal techniques employed for approximate equivalence checking into a search-based circuit optimization algorithm based on the Cartesian Genetic Programming. The key idea of our approach is to employ a novel search strategy that drives the search towards promptly verifiable approximate circuits. We evaluated the method's performance on functional approximation of multipliers (with up to 32-bit operands) and adders (with up to 128-bit operands). This is for the first time when such complex approximate circuits with formal error bounds have been presented, which demonstrates an outstanding performance and scalability of our approach compared to the existing methods that have either been applied to the synthesis of 8-bit multipliers or a statistical testing has been used only. Our approach thus significantly improves capabilities of existing methods.

The thesis is organized as follows. Chapter 2 includes basic information about approximation techniques, evolutionary algorithms and describes the chosen method – Cartesian Genetic Programming – in detail. Chapter 3 discusses the formal methods that can be employed for the evaluation of the features and qualities of approximate circuits. In Chapter 4 we propose novel miter constructions and the key feature of this project – verifiability driven search strategy – that greatly increases the algorithm's performance. Chapter 5 overviews the most important aspects of the implementation of the algorithm in ABC. Chapter 6 is dedicated to experiments and statistical testing of the developed implementation. During the experiments, we constructed a high-quality Pareto set of multipliers up to 32-bit providing trade-offs between the circuit error and size. The best circuits were synthesized into target 45 nm technology and their nonfunctional parameters (such as on-chip area or power consumption) were examined.

# Chapter 2

# Evolution Based Approximate Circuit Design

Initially, the approximate circuits were designed manually by removing parts of the existing fully functional designs that were not significantly contributing to the result. For example, during the development of approximate adders or multipliers we can save some on-chip area by removing the logic computing the least important bits of the result. This approach is naive and very simple. However, it does not provide interesting results and more complex techniques are needed to achieve further improvements. In this thesis, we focus on the approximate circuit design using evolutionary algorithms which are described in this chapter.

## 2.1 Approximation techniques

There are three basic approaches to the implementation of approximate circuits [19]:

- over-scaling,

- over-clocking,

- functional approximation.

The over-scaling and over-clocking techniques use ordinary circuits that work perfectly fine under usual circumstances. The first method can reduce power consumption by voltage over-scaling, which can cause the occurrence of occasional errors. Similarly, over-clocking can achieve greater performance by enhancing circuit's working frequency over the maximum frequency at which the circuit still works correctly. This leads to the occurrence of timing errors, but better overall performance.

Unlike the first two methods, functional approximation does not use the original correct circuit but rather a specially created one. This circuit is designed in such a way that it does not fully implement the original logic behavior described in the specification. The simplest method that was already mentioned in the previous section implements functional approximation by omitting the least significant bits of the result and removing related logic. Small approximate circuits can also be designed manually with very good outcome. For example, a two-bit approximate multiplier which was manually constructed consists of 5 gates only and exhibits the delay of 2 d where d is a unit delay of logic gate. Its output is correct for 15 out of 16 possible inputs. A conventional solution requires 8 gates and

exhibits the delay of 3 d. This approximate multiplier has been used in larger multipliers and then employed in image processing applications. Reported power savings are impressive: 30%-50% for a mean error of 1.39% - 3.35% [10].

The manual design of circuits on gate level is only possible for very small circuits. For larger circuits the task becomes unfeasible. Advanced techniques employ the automatic logic synthesis of new approximate circuits whose error must not exceed predefined limit. Measuring the error of the approximate circuit requires expressing its error by one of various metrics such as worst case error, error rate, mean error, etc. Some synthesis tools try to derive the approximate circuit from the original one, other methods use different heuristics and metaheuristics to design the demanded circuit. This thesis focuses mainly on the technique of circuit design called evolutionary algorithms. This metaheuristic, its versions and related topics are described in detail in the following sections of this chapter.

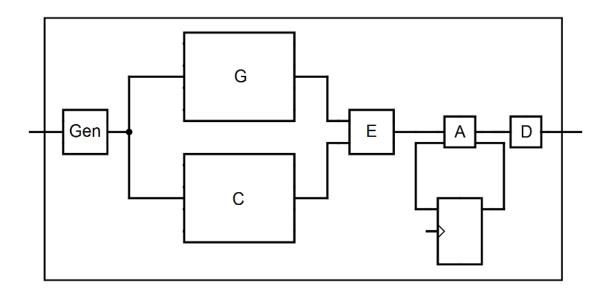

## 2.2 Evolutionary algorithms

Generally, an evolutionary algorithm is a metaheuristic technique for solving optimization and search problems inspired by the natural selection and evolution of living organisms. It can also be used for the design of both software and hardware systems [12]. The search space consist of all possible solutions, each element of this space represents a specific solution. A computer program, or in our case a logic circuit, is encoded as a set of genes. These genes are then modified using genetic operators to explore the space of possible solutions. Evolutionary algorithms usually work in generations. In the beginning there is a set of initial candidate solutions (first generation), generated either randomly or seeded. The solutions are then evaluated by a metric called fitness function which describes the quality of each solution. A set of the best solutions is chosen and used by the evolutionary algorithm to create a new generation of solutions and the whole process is repeated. This task is iteratively done until a predefined number of generations is reached or a solution with sufficient quality is found.

When applying genetic algorithms to a specific problem, there are two essential tasks to be solved. The first one is to encode the candidate solutions in such a way that allows us to combine and modify them to create new candidate solutions with different features and qualities. Secondly, we have to be able to asses the quality of a candidate solution and decide which solution from a set is the best one. There are many known formats for the representation of different optimization or search problems, some of them are mentioned in the list bellow. The gene representation is sometimes also called a chromosome.

- Bit vectors,

- integer or floating point number vectors,

- graphs,

- trees.

Creating new generation of solutions from the previous ones is performed by the means of genetic operators. There is a great variety of them and their form depends on selected gene representation of the candidate solutions. The most common operators include:

- vector crossover (one point, multipoint, uniform),

- tree crossover,

mutations.

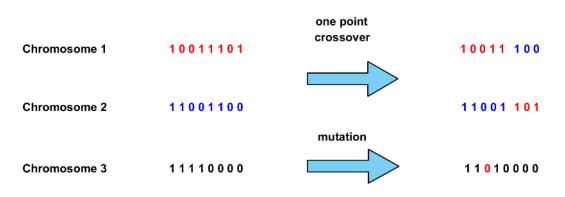

Crossover (also recombination) usually combines two chosen candidate solutions, called parents, into one or more new solutions, offspring. Mutations choose one candidate solution and perform a slight change on it in order to preserve most of its useful features in the next generations. Typical examples of mutations include flipping a bit value in a bit vector, randomly increasing or decreasing value in integer vectors and swapping or creating nodes in graphs or trees. Examples of these operators performed on 8-bit vectors are illustrated in Figure 2.1

Figure 2.1: Crossover and mutation of binary vector chromosomes.

Evolutionary algorithms are applicable in many different areas of optimization and search problems and its specific form depends heavily on actual application. One alternative that is very useful in designing combination digital circuits on the gate level and thus for the goal of this thesis is called the *Cartesian Genetic Programming* (CGP). This method can be successfully used for the approximate circuit development and is further described in the section below.

### 2.3 Cartesian genetic programming

Cartesian genetic programming [11] is one variant of the various evolutionary algorithms. It encodes solved problem in a form of oriented acyclic graph. Each node of the graph represents elementary function (logical *and*, *or*, *xor*, etc.) from a predefined set of functions.

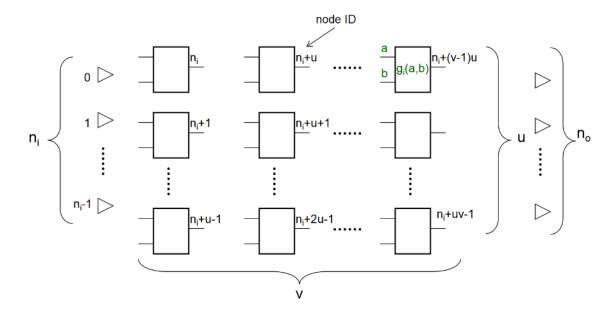

Nodes of the graph are connected by oriented edges. Each node has  $n_a$  input edges and one output value that can be assigned to its output edges. The whole graph has  $n_i$ primary inputs and  $n_o$  primary outputs. The nodes of the graph are arranged in a regular two dimensional matrix of fixed size with u rows and v columns. This representation is favorable because it resembles the organization of logic gates in digital circuits and the structure of elements in FPGAs. A generic CGP matrix along with its parameters is shown in Figure 2.2.

Every node's inputs can be connected to either primary inputs or outputs of the nodes in previous columns. Node's outputs can serve as inputs for the nodes in following columns or outputs of the whole graph. Connections between nodes in the same column are forbidden. So called L-back parameter defines the number of previous columns that can be used as inputs for a specific node. For example with the L-back parameter set to 2, a node in the fourth column can use outputs from the second and third columns but cannot be connected to the outputs of the first column nor the primary inputs. L-back set to 1 allows only the usage of the previous column and is convenient for developing circuits with pipeline processing. L-back set to maximum value (number of columns) enables maximum connectivity and thus the biggest variety of solutions.

Definition of CGP parameters:

- number of rows, u,

- number of columns, v,

- number of inputs,  $n_i$ ,

- $\bullet\,$  number of outputs,  $n_o,$

- number of each node's inputs, n<sub>a</sub>,

- L-back parameter, L,

- set of available functions, F,

- $\bullet\,$  number of available functions,  $n_{\rm f}.$

Figure 2.2: Basic scheme of CGP representation.

One of the main advantages of CGP is that it prevents the occurrence of the so called *bloat* phenomenon. During the evolution we usually try to encourage modifications of candidate solutions. When comparing the best solution obtained so far to the new generation of solutions we always prefer the new solution to the old one in case they are equal. This approach allows us to explore areas of the state space of chromosome that would otherwise be unreachable. On the other hand, the selection of new modified candidate solutions also leads to the bloat. As the generations proceed, the chromosome develops ineffective or redundant parts, which are always accepted and passed to further generations. The chromosomes grow larger and larger and their processing slows down significantly. In past, the size of the chromosome could even exceed the memory capacity of the host computer. CGP does not suffer from the bloat because of fixed chromosome length which is limited by the size of the node matrix. Thanks to this we can perform much more generations of evolution than in the classic genetic programming without running into the bloat problem.

### 2.3.1 Chromosome representation

Another advantage of Cartesian genetic programming is its simple and compact format of chromosome representation. It can be easily encoded as a fixed length integer vector, as shown in the following example. This representation also allows us an easy manipulation of the chromosome during the creation of new candidate solutions and will be demonstrated on the example in Section 2.3.2.

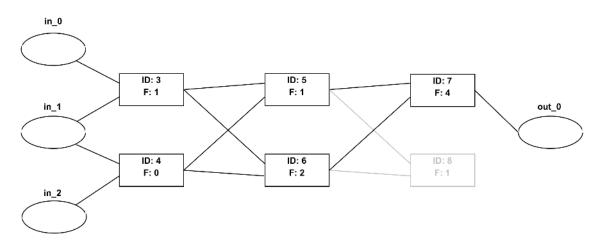

Figure 2.3: Example of CGP circuits representation.

In the Figure 2.3 we can see a simple example of a digital circuit developed using CGP with the following parameters:

- $\bullet \ u=2, \qquad \bullet \ n_a=2,$

- v = 3, L = 1,

- $n_i = 3$ , F = [and, or, nand, nor, xor],

- $n_o = 1$ ,  $n_f = 5$ .

The example circuit consists of standard two input logic gates and has three primary inputs and one output. The matrix of nodes has two rows and three columns, six function nodes in total. As we can see, not all of the nodes in matrix necessarily have to contribute to creating the output value. This gives the evolution the space to create various solutions with different qualities (number of nodes, delay, used functions, etc.). The unused node and connections are marked grey in the example picture.

The chromosome representation consist of  $u^*v$  triplets (u – number of rows, v – number of columns) of integer values, where the first two values entail the identification of the ouputs connected to the first and second inputs of the corresponding element. The third value in the triplet represents the logic function realized by the node. This value is used as an index into the list of used functions F. At the end of the chromosome there is a tuple of the same size as the number of circuit's primary outputs. This tuple defines, the connections to primary outputs. The beginning of the chromosome can optionally contain a tuple stating the number of primary inputs and outputs, the size of the matrix and other optional information, too. The example circuit is encoded in the chromosome as a list of integers as follows. Triplets for each node are enclosed in brackets for a better readability.

(3, 1, 3, 2), (0, 1, 1), (1, 2, 0), (3, 4, 1), (3, 4, 2), (5, 6, 4), (5, 6, 1), (7)

The first four values give basic information about the circuit. Next triplets represent one node of the matrix each. For example, the highlighted triplet has its two inputs connected to the primary inputs 1 and 2. Its function has index 0 and thus the function of the node is logical AND. The last value defines, that the circuit's only primary output is connected to node number 7.

### 2.3.2 Genetic operators

During the evolution with Cartesian Genetic Programming, only one of the above mentioned genetic operators is used – mutations. The other operators have not brought any interesting results. In each generation, we perform mutations on the best candidate solution found so far. The mutations affect only a small part of chromosome (one or a few integer values). The area of the chromosome to be mutated is usually randomly chosen.

During the mutations, it is vital to respect the given parameters of the circuit – the size of the matrix, L-back parameter and the number of functions available. For instance, when mutating node ID 8 – (5, 6, 1) – from the example above, we can only insert values 5 or 6 as its inputs because of L-back parameter set to 1. When changing its function, we can use values 0 to 4 since we have 5 functions available altogether.

### 2.3.3 CGP pseudocode

The whole process of Cartesian genetic programming can be described by the following algorithm written in pseudocode. In the code we can easily determine the key factors relevant for the algorithm performance. These will be discussed in the next section.

| Algorithm 1 Cartesian Genetic Programming pseudocode.       |  |  |  |  |  |

|-------------------------------------------------------------|--|--|--|--|--|

| Input: CGP configuration parameters, termination criterion. |  |  |  |  |  |

| 1: Randomly generate parent p.                              |  |  |  |  |  |

| 2: Generate $P$ offspring of $p$ using mutations.           |  |  |  |  |  |

| 3: Evaluate the population.                                 |  |  |  |  |  |

| 4: while The termination criterion is not satisfied do      |  |  |  |  |  |

| 5: Select the highest scoring offspring $b$ .               |  |  |  |  |  |

| 6: <b>if</b> fitness(b) $\geq$ fitness(p) <b>then</b>       |  |  |  |  |  |

| 7: $p \leftarrow b$                                         |  |  |  |  |  |

| 8: Generate <i>P</i> offspring of <i>p</i> using mutations. |  |  |  |  |  |

|                                                             |  |  |  |  |  |

```

9: Evaluate the population.

```

10: return Best candidate found p.

### 2.4 Fitness function and error metrics

During each generation cycle of Cartesian Genetic Programming (and evolutionary algorithms in general), we need to evaluate the quality of candidate solutions in order to determine which one is the best solution for the problem given. To accomplish this task, we use a fitness function that takes a candidate solution and assigns it a value representing its quality (fitness). The result tells us how closely the specific candidate solution gets to satisfy set aims. In cases where a golden solution of a problem is available, fitness function usually compares the results of a candidate solution to the outputs of the golden solution and the fitness defines, how similar these outputs are. In cases without known golden solution, we need to use a suitable heuristic or approximation. The fitness function can take multiple criteria into account. For example, after achieving a certain precision of the candidate solutions, we can then focus on minimalizing the on-chip area (number of logic gates) of the solution or its logic delay.

The most common fitness function for combination digital circuits, such as adders, multipliers or multiplexors, is the Hamming distance (HD). In this case we evaluate the candidate solution for all possible input combinations and compare its output to the corresponding results of a golden solution (i.e. correct multiplier). The fitness function computing the Hamming distance determines the number of bits where the two compared results differ. Our goal during the evolution is to minimize the value of the fitness. When a solution with zero fitness function is found, we can either end the evolution or focus on other criteria of the solution as was described above.

Hamming distance as the fitness function is simple and useful; approximate arithmetic circuits have different demands, however. HD can be still applied to circuits as multiplexors or decoders, but it does not reflect the qualities of arithmetic circuits (adders, multipliers) well. For example, a candidate multiplier can only have 2% of different bit values in its outputs compared to the correct multiplier, but if the errors occur on the most significant bits, the results do not correspond to the correct outputs at all. That's why we need to employ arithmetic error. This type of error is more demanding in the terms of computational resources, because we need to interpret the output values as numbers and perform arithmetic operations to measure the error. These operations are slower than the bitwise operations for the computations of plain Hamming distance. There are different error metrics we can use to determine the error of an arithmetic circuit:

- total error sum of absolute values of errors for all input combinations,

- error rate the number of input combinations that give wrong result,

- worst-case error the highest error occurring among all input combinations,

- average error.

These metrics can be used to determine the quality of an approximate circuit and hence as the fitness function during CGP evolution. There are various demands on the solutions we can achieve by applying multi-criteria fitness function with the error metrics, i. e. an approximate adder that generates correct output in 95 % of cases, has a minimal average error and covers minimal area on chip, or an approximate multiplier with minimal delay whose error never exceeds a predefined value.

In this thesis, we focus mainly on the worst-case error and the mean average error and define them as follows. For a correctly working circuit G (golden solution) which computes

a function  $f_G$  and its approximation C (candidate solution) computing a function  $f_C$ , where  $f_G, f_C : \{0,1\}^n \to \{0,1\}^m$  (*m* and *n* are positive integers denoting the input and output bit widths) are formulated:

WCRE

$$(G, C) = \frac{\max_{x \in \{0,1\}^n} |\operatorname{int}(f_G(x)) - \operatorname{int}(f_C(x))|}{2^m},$$

MAE $(G, C) = \frac{\sum_{x \in \{0,1\}^n} |\operatorname{int}(f_G(x)) - \operatorname{int}(f_C(x))|}{2^m},$

where int(x) denotes the integer representation of the bit vector x and |i| denotes the absolute value of the integer *i*.

### 2.4.1 Fitness evaluation methods

The total time needed to complete a whole evolution cycle can be defined as:

$$T = G * \left( (T_a + T_c) * P + T_p \right)$$

- G number of generations,

- T<sub>a</sub> time of evaluation of a candidate solution,

- T<sub>c</sub> time needed to compare fitness values of candidate solutions,

- T<sub>p</sub> time for the generation of new population,

- P the size of population.

Generating a new population of candidate solutions by the means of mutation and comparison of fitness values are relatively quick and easy. On the other hand, evaluating the fitness function is very demanding and often makes up most of the computational time. The Cartesian Genetic Programming usually needs a high number of generations to evolve a working circuit (millions of generations). In every generation, we need to assess the quality of every candidate solution. The speed of fitness function evaluation is hence crucial for the successful circuit development.

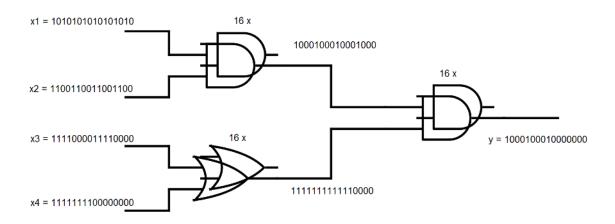

One of the methods to speed up the fitness evaluation capitalizes on the fact that present processors perform bitwise operations on whole 32 or 64 bit registers. Instead of evaluating one input combination at a time, we can speed up the whole process up to 64 times. In each cycle, we fill the registers with 64 different input values and evaluate fitness for all of these values in parallel. The whole process is demonstrated in Figure 2.4.

Even with this significant acceleration, the speed of fitness evaluation is still not sufficient for designing circuits with a large number of input combinations. One of the solutions to this problem can be performing evaluation of only a small random part of the possible input combinations (random simulation). However, this approach only approximates the candidate's fitness and does not guarantee its exact value. This thesis focuses on a different kind of approach that relies on formal methods to prove the features of a candidate solution. The next chapter aims at these methods and discusses them thoroughly.

Figure 2.4: An example of parallel fitness evaluation with 4 input variables

# Chapter 3

# Formal Methods for Fitness Evaluation

Developing larger and more complex circuits with CGP becomes very demanding for three main reasons. Firstly, with growing size and complexity, the evaluation of circuit's outputs takes longer time for every input combination. Secondly, the number of possible input combinations, and thus the time complexity, grows exponentially with the number of inputs. For example, for a 3 bit adder, we need to evaluate  $2^6$  different input combinations, in case of 4 bit adder, the number of possible inputs grows to  $2^8$ . The third and final reason is that with increasing complexity of the circuit the length of its chromosome increases as well. This means that the state space of the problem to be examined by the evolutionary algorithm grows in size and we need to perform more cycles of the algorithm to successfully explore it.

As we can see, the problem to solve has two major points. We need to execute more evaluations of the candidate solutions, but at the same time each evaluation takes longer. The combination of these problems makes the classic evolution design of circuits with input bit widths bigger than 8 bits unfeasible. In order to achieve satisfactory results, we need to speed up the evaluation of candidate solutions and/or improve the search algorithm.

One of the goals of this thesis is to examine the techniques improving the speed of the fitness computation. Instead of the iterative evaluation of all input combinations, we transform the problem into a formal query describing circuit's features and then try to prove them or find a counter example disproving them. This chapter discusses various formal verification methods that can possibly be used in the previously described approach.

## **3.1** Basic verification techniques

There are lots of various formal verification techniques. In this thesis, we focus mainly on automated methods that can be potentially utilized for the evaluation of the quality (fitness) of the candidate approximate circuits.

### 3.1.1 Explicit Model Checking

Model checking [6] (also property checking) is a problem of determining whether a given system meets a defined specification. This is accomplished by a systematic exploration of the state space of the system. The systems in question are usually finite state. The systems are typically hardware or software and the specification contains safety requirements such as the absence of deadlocks and other critical states that can cause the system to crash. In order to solve this problem automatically, we need to express both the system and the specification in a precise mathematical language. The system to be verified is usually modeled as a finite state machine and the reachable states of this machine are then traversed in order to verify the properties.

The properties are classically specified using temporary logics (LTL, CTL, CTL<sup>\*</sup>, ...), but there are also other forms possible. The properties checked are generally classified as *safety* and *liveness* properties. While the former declares what should not happen (e.g. deadlock), the latter declares what should eventually happen (e.g. system always eventually responds to a message). A counterexample for a safety property is a sequence of states where the last state contradicts the property. A counterexample to liveness properties is a path to a loop of states that does not contain a desired state. Such a loop represents an infinite path that never reaches the specified state.

The advantages of model checking include:

- a high degree of automation,

- easiness of use,

- generality,

- provides counter examples.

On the other hand, the model checking is held back by the problem of the state space explosion. The number of possible states of a specific system grows rapidly as a result of combinatorial considerations. For example, a system with two 32 bit variables can be in  $2^{32} * 2^{32}$  different states when only considering these two variables. Another cause of the state explosion is interleaving of concurrent processes – n concurrent processes with m states can generate  $m^n$  states! Considering these facts we can see that for almost every practical system the state space gets easily out of proportion and its exploration becomes computationally unfeasible. There are various techniques of dealing with the state space explosion problem, such as:

- efficient storage of state space, symbolic model checking,

- state space reductions (symmetries, partial order reduction),

- abstraction,

- compositional methods,

- bounded model checking.

### 3.1.2 Symbolic model checking

The symbolic model checking [4] made a breakthrough towards wide usage of these techniques. In symbolic model checking, the sets of states are represented implicitly using Boolean functions. For example, we can assume that the behavior of a system is determined by two binary variables  $v_1$  and  $v_2$  and that (11, 10, 01) are the three combinations of values that can be assigned to these variable in any run of the system. Rather than keeping explicit list of these states (as was done in explicit model checking), it is more efficient to handle a Boolean function, that represents this set, i. e.  $v_1 \vee v_2$ . Manipulating Boolean functions can be easily done with the application of Reduced Ordered Binary Decision Diagrams [3] (ROBDDs), a compact, canonical graph representation of Boolean functions.

The initial set of states is represented as a ROBDD. The procedure then starts an iterative process where, at each step i, the set of states that can be reached for the first time in i steps from the initial states are added into the ROBDD. At each step, the set of states is intersected with the set of states that satisfies the negation of the property. If the result of the intersection is a non-empty set, an error has been detected. The procedure ends, when the set of newly added states is empty or an error is found. The first case indicates that the property is satisfied, because no reachable states violates it. The latter case generates an counterexample of an incorrect run of the system.

The bottleneck of these methods is the amount of memory that is required for storing and manipulating ROBDDs. The Boolean functions representing the sets of states can grow exponentially. There are many techniques such as abstraction, reduction and decomposition to solve this problem, but the state explosion is still not overcome.

It has been shown that BDDs can be utilized in the design of approximate adders [24] but are not suitable for the development of approximate multipliers. Alternatively, symbolic model checking can be encoded into the boolean satisfiability problem (SAT). This approach is suitable for circuit design and will be described in detail in the next section.

### 3.2 Verification through satisfiability checking

### 3.2.1 SAT

Boolean satisfiability problem (SAT) is the problem of determining, whether there exists a variable assignment (interpretation) for a given propositional formula such that the formula evaluates to true. In other words, we ask whether a given Boolean formula can evaluate to true. If such assignment exists, the formula is called satisfiable. On the other hand, if there is no such interpretation, we say that the formula is unsatisfiable.

$$a \wedge \neg b \wedge c$$

(3.1)

$$a \wedge \neg a$$

(3.2)

Formula 3.1 is satisfiable because there exists the interpretation a = true, b = false, c = true and the whole formula evaluates to true. Formula 3.2 is unsatisfiable because in every possible interpretation the formula always evaluates to false.

SAT is a known NP-complete problem [7]. This means that there is no algorithm that efficiently solves all SAT instances. However, NP-completeness does not exclude the possibility of finding heuristic algorithms that solve interesting practical SAT instances well. These instances come from various areas, such as automatic theorem proving, circuit design, artificial intelligence and software verification. Because of its wide areas of application, SAT has been subject to intensive research and there are many SAT solving tools and algorithms.

#### Formula representation

Usually, we consider a propositional formula given in the Conjunctive Normal Form (CNF). Such formula consists of conjunction (logic and) of clauses where a clause is a disjunction (logic or) of literals. Literal is a propositional symbol with optional negation. Every propositional formula can be converted to an equisatisfiable formula in CNF using the Tseitin transformation [21].

$$(a \lor \neg c \lor d) \land (a \lor \neg b \lor c) \land (\neg a \lor \neg d)$$

$$(3.3)$$

In the example Formula 3.3,  $(a \lor b \lor \neg c)$  is a clause,  $\neg a$  is a literal and a is a propositional symbol. Propositional formulas in CNF are usually represented in a format called DIMACS. This ASCII format is simple for automatic parsing and at the same time readable for humans. Its first line contains information about the number of clauses and the number of variables (propositional symbols) in the form p cnf nbvar nbclauses. After that the clauses follow, each one on separate row. Each clause is a sequence of non-zero integer numbers from the interval < -nbvar, nbvar > ending with 0 on the same line. The positive numbers denote corresponding variables, negative numbers mean negation of the corresponding variables. The following example of the DIMACS format shows the encoding of Formula 3.3. The numbers are assigned to the variables in alphabetical order.

p cnf 4 3 1 -3 4 0 1 -2 3 0 -1 -4 0

### SAT solving

Most SAT solving tools are built on variants of the classical Davis-Putnam-Longemann-Loveland (DPLL) procedure. This algorithm starts from the ground CNF formula and tries to build an assignment that satisfies the formula and hence proves that the formula is satisfiable. This assignment is created using a backtracking mechanism.

The DPLL procedure works over an abstract DPLL system. This system is a pair  $(S, \Rightarrow)$  where S is a set of states and  $\Rightarrow$  is a set of transitions between the states. Each state is a pair denoted M||F where M is an assignment and F is a formula to be verified. There is also a special labeled state *fail*. The procedure starts from the initial state  $\emptyset||F$  and builds the assignment using the following, briefly described rules.

- PureLiteral we add literal l to M if F contains l, F does not contain  $\neg l$  and l is undefined in M.

- Decide we add literal l<sup>d</sup> to M if l or ¬l occurs in F and l is undefined in M. Index d denotes that this literal is a decision literal and was put into the assignment by the Decide rule.

- UnitPropagate we add literal l to M if F contains a clause C that has all literals but l defined in M and is still not satisfied.

- Backtrack when the formula F becomes unsatisfiable with the current assignment M, we return to the first decision literal in M, negate its value and remove its decision index. All the literals put into the assignment after the actual decision literal are deleted.

- Fail we enter the fail state if F is unsatisfiable with the assignment M and M contains no decision literal. This means the formula is unsatisfiable.

Opposite to the fail rule, if there is no other rule applicable and the derivation has not got to the fail state, the given formula is satisfiable. The assignment in the final state of the procedure is an example of satisfying assignment for the formula. The rules are not applied in random order but rather according to a priority scale. Firstly, Backtrack or Fail are applied if applicable. Otherwise, PureLiteral or UnitPropagate are applied if possible. At last, if no other rule is applicable, we use the Decide rule. The motivation of placing Decide to the lowest priority is to reduce the amount of guessing as much as possible. The Decide procedure can be subject to many various and complex heuristic that can significantly affect the performance of the algorithm.

Modern DPLL systems do not use PureLiteral rule in the derivation process but rather perform this task as a preprocessing step. Additionally, a more efficient backtracking algorithm is used. Simple Backtrack method often goes back to irrelevant decision points and then performs the same steps until the solution fails again. This can happen multiple times and leads to useless back and forth computations. Instead, the more efficient BackJump rule analyses the clauses and conflicts in the assignment, skips multiple decision levels and jumps directly to the relevant decision point. These systems can also learn new clauses that do not affect the satisfiability of the formula, but can speed up the algorithm. On the other hand, some unnecessary clauses can be neglected too.

### 3.2.2 SMT

Satisfiability modulo theories (SMT) [1] problem is a decision problem for logical formulas with respect to background theories expressed in the classical first-order logic with equality. This problem extends SAT by providing more information about the meaning of logical formulas in the supporting theories. In computer science, these theories can typically include the theory of real numbers, theory of integers and the theories of various data structures such as arrays, lists, bit vectors, uninterpreted functions, etc.

SMT instance is a formula in first-order logic, where the function and predicate symbols have additional interpretation and like in SAT, the problem is to determine whether such formula is satisfiable.

There are different approaches to solving SMT. The *eager SMT techniques* take advantage of existing SAT solvers. Firstly, we translate the input logical formula F into a satisfiability-preserving propositional formula F'. Then we can use SAT solver to determine, whether the new formula F' is satisfiable. This approach is not used in practice very often. We need specific translation methods for each theory and the technique might quickly run out of time or memory in many practical applications. There is also the lazy approach with a much better performance.

The *lazy SMT techniques* split the task of the decision procedure into two co-operating parts:

- a propositional SAT solver, which checks the satisfiability of the boolean skeleton of the formula given and views atomic formulas as simple propositional symbols,

- a theory solver, which implements decision procedure for the given theory T.

The first step is to build a dictionary of atomic predicates that appear in the input formula F. We also need to recognize their positive and negative appearances. The first row in the following table lists atomic predicates occurring in Formula 3.4, the second row assigns the propositional symbols for SAT solver to the predicates. Note the positive and negative occurrence of predicate  $p_1$ .

$$(a > 1 \lor b < 5) \land (a \le 1 \lor b > 2) \land (c \ge 5)$$

(3.4)

| a > 1 | b < 5 | $a \leq 1$ | b > 2 | $c \ge 5$ |

|-------|-------|------------|-------|-----------|

| $p_1$ | $p_2$ | $\neg p_1$ | $p_3$ | $p_4$     |

The typical lazy SMT decision procedure uses the following interaction of a SAT solver and a T-solver for a single theory involved:

- 1. SAT solver checks whether the boolean skeleton of the input formula is satisfiable. If it's not, then F is also T-unsatisfiable and the procedure terminates. Otherwise, the procedure continues with the next step.

- 2. SAT solver finds a satisfying assignment M for the boolean skeleton of F. The theory solver then checks, whether T(M) is satisfiable. If it indeed is, the formula is T-satisfiable and the procedure ends with this result. Otherwise, we cannot yet decide the satisfiability of F and the procedure continues.

- 3. The theory solver provides a theory lemma which is added to the set of clauses. The SAT solver is then restarted and the whole process begins again from step 1 with the updated set of clauses.

The basic lazy SMT approach has various extensions that improve its performance, memory demands, etc. These extensions include *on-line* SAT solver (after a restart, solver does not begin from empty assignment, but continues from the current one with updated set of clauses) and *incremental* SAT solver (SAT solver can query T-solver during the SAT decision procedure and does not have to wait until a satisfying assignment is found). When dealing with more than one background theory, more complicated approaches are needed, such as the Nelson-Oppen method [17].

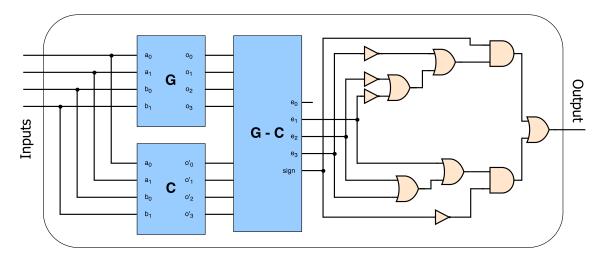

### 3.3 Strict equivalence miters

In order to successfully employ formal verification methods for the evaluation of the fitness function in CGP, we cannot work with the candidate solutions in their chromosome form. We need to transform the representation into logical formulas (propositional or first order for SAT or SMT respectively) or create a formal model for them to be model checked. Moreover, we also need to specify the proper behavior we are trying to achieve.

In case of using a SAT solver, which this thesis aims at, we need to encode the comparison of the candidate solution and the golden solution into a propositional formula. This formula is then examined by the SAT solver which gives us the result, whether or not the candidate solution satisfies the specification. This can be done by connecting the candidate and the golden solution with a special construction called a *miter*.

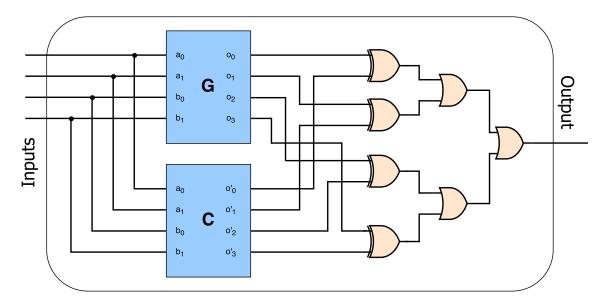

In our case, the basic miter is a combinational circuit that checks the equivalence of the two solutions in question. These have equivalent behavior if and only if their output values are always the same for any corresponding input values. Comparison of corresponding output bit values can be done easily by connecting them to a newly constructed logical XOR gate. This gate is added to every pair of equivalent outputs of the circuits. After that, to check whether the output of any of the new XOR gates evaluates to the state of logical '1', we perform logical OR on their outputs. Because the number of circuit's outputs is arbitrary and there are usually only two input gates available, we build a tree of OR gates over the XOR gates. The output of the root of the tree indicates, whether the two circuits are equivalent or not.

Figure 3.1: Miter checking the equivalence of two circuits.

Figure 3.1 illustrates an example of miter constructed over two 4 bit output circuits. The candidate solution and the golden solution are labeled C and G respectively. XOR operation is performed over every pair of corresponding output bits and their value is then aggregated using OR gates. The comparison of the same input combinations is ensured by the connection of the corresponding input ports to the same input wires.

The whole circuit is combinational and consists only of standard logic gates. Thus, it can be easily converted into a propositional formula. As was already stated above, most SAT solvers work with formulas in the Conjunctive Normal Form (CNF). A general formula can be converted into CNF using the Tseitin transformation [21]. The value of this formula for a given assignment (values of input variables) represents the value of the circuit's single output. In order to solve the equivalency problem, we need to include both the candidate solution and the golden solution into the propositional formula. Moreover, it also has to contain some additional logic for the miter. This results into a rapid growth of the formula and need for an efficient SAT solver. Current solvers are well capable of checking formulas with tens thousand of variables and are able to verify complex combination circuits, such as 16 or 32 bit multipliers.

The SAT solver checking the propositional formula can return one of two possible results – the formula is either satisfiable or unsatisfiable. Unsatisfiability of the formula says, that the output of the circuit always preserves the logic '0' value. This means that none of the XOR gates over the outputs of the golden and candidate solutions ever gets into logic '1' state and thus all the outputs are always equivalent. On the other hand, satisfiability of the formula shows, that the outputs of the examined circuits differ for some input combinations and the circuits are not equivalent.

This miter checks only the strict equivalence of circuits and offers no information about their similarity. That's why it is not suitable for the approximate circuit development. For this task, we need to design different miters that will help us measure the various error metrics described earlier. Section 3.4 focuses on such miters.

### 3.3.1 ABC

The ABC synthesis tool [13] is an open source software for synthesis and verification of binary combinational and sequential circuits. The main purpose of ABC is to create an academic synthesis tool with its strength equal to common commercial tools. It provides implementations of formal verification and optimization algorithms as well as various formats and functions for circuit synthesis and manipulation. This makes it a suitable tool for the purposes of this thesis. One of the drawbacks of ABC is the absence of documentation, which makes adding new features to the tool challenging. Because of the useful procedures and methods, ABC is suitable for the realization of the algorithm proposed in the next chapter. The algorithm is implemented as one of the modules of the tool and is accessible directly from the ABC command line interface.

ABC provides methods for the basic strict combinational equivalence checking. To examine whether two combinational circuits are equivalent, ABC constructs the previously described miter including the two circuits. The tool then uses one of the inbuilt satisfiability check procedures to examine the satisfiability of the miter's output.

#### Circuit representation formats

The basic format for circuit representation, manipulation and optimization in ABC is AIG (and-invertor graph). This format represents circuit as an acyclic graph, each node of the graph has the function of logical AND with two inputs. The nodes are connected by edges with arbitrary invertor signs. This basic version of AIG can be extended to sequential AIG by adding another labeling function to the edges marking the count of the registers along an edge. AIG a is very efficient format of representation because of its simplicity, ease of manipulation and the existence of the compact binary AIG format for exporting the circuits.

Apart from AIGs, ABC supports other representation formats, such as netlist, logical network, binary decision diagrams and technology mapped network (FPGA look up tables, a set of gates). ABC can also read input files in various formats (Verilog, BLIF, PLA, EDIF, BAF, truth table, etc.).

### Implemented tools, functions and algorithms

The functions implemented in ABC can be divided into following categories.

- Input and output reading and writing different circuit representation formats.

- Combinational synthesis starts with an AIG representation or SOP network. Then can perform optional optimizations using rewriting, renoding and redundancy removal. Finally performs the logical synthesis into simple netlist consisting of logical gates defined in cell library.

- Sequential synthesis similar to combinational synthesis, using also registers and latches. Can also perform retiming to achieve better performance of pipelined circuits.

- Technology mapping look up table mapping into FPGAs or standard cell mapping.

- Verification commands can perform strict equivalency check of two circuits or build a miter over them. Also features SAT solver implementation and thus can examine the satisfiability of a circuit's output. This area of functions does not include any relaxed equivalency checks, these have to be further implemented.

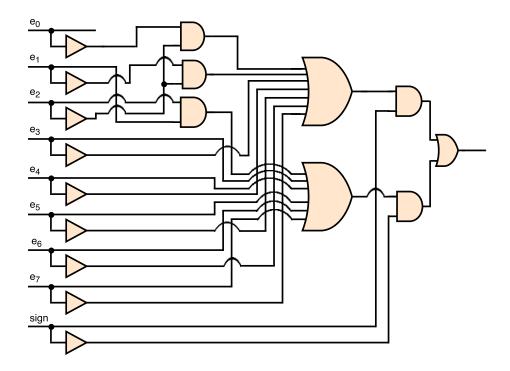

### **3.4** Approximate equivalence miters

The simple miter shown in the previous section is not suitable for our purposes because it only checks the strict equivalence. In order to compare two circuits with regards to a chosen error metric, we need to rely on more complex miters. Their design, implementation and comparison is one of the aims of this thesis. In this section, we provide an overview of existing miters, their features and utilization.

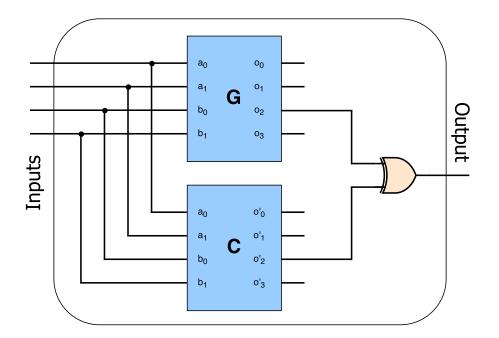

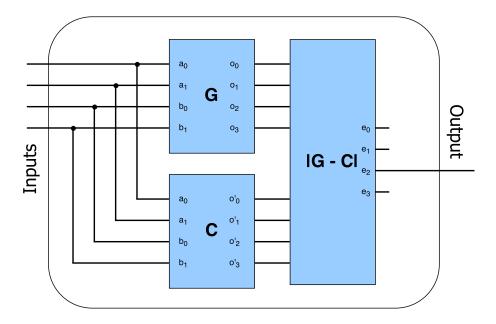

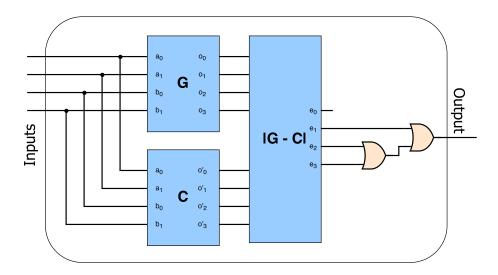

### 3.4.1 N-th bit error

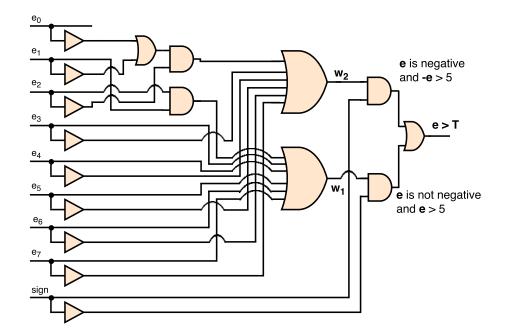

The simplest miter checking the degree of two circuits equivalence can be constructed by checking the equivalence of each corresponding bit of their outputs separately. We start from the most significant bit, create the miter and perform the check using a SAT solver. If the formula is not satisfiable (the outputs are the same for all possible input combinations), we iteratively go downwards to the least significant bit. The procedure is stopped at the first output bit that is not equivalent. This is the most significant bit of the candidate solution that differs from the golden solution. The index of this bit in the result of the circuit is i, assuming that the least significant bit has index 0. The maximal arithmetic error of the candidate solution therefore does not exceed  $2^{i+1}$ . The example of such a miter is shown in Figure 3.2.